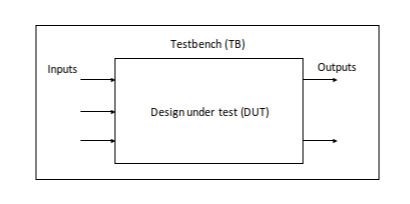

이 테스트벤치는 디지털 회로를 시뮬레이션하고 검증하기 위한 코드입니다. 디지털 회로는 하드웨어 자체적으로 테스트하기 어려운 경우가 많아서, 테스트벤치를 작성하여 시뮬레이션을 수행하고 회로의 동작을 확인합니다.

또한 입력 신호를 생성하고, 이를 디지털 회로에 적용하여 출력 신호를 측정하고 검증합니다. 이를 위해 테스트벤치는 주어진 입력에 대한 예상 출력을 정의하고, 디지털 회로가 예상 출력과 동일한지를 확인합니다.

library ieee;

use ieee.std_logic_1164.all;

entity half_adder is

port (a, b : in std_logic;

sum, carry : out std_logic

);

end half_adder;

architecture arch of half_adder is

begin

sum <= a xor b;

carry <= a and b;

end arch;이코드는 하프에더의 vhdl code입니다. 두개의 입력(a,b)과 두개의 출력(sum,carry)을 가지고있습니다.

sum은 xor연산자를 이용하여 계산되며, carry는 and연산자를 이용하여 계산됩니다.

다음은 이 하프에더의 테스트 벤치 코드입니다.

library ieee;

use ieee.std_logic_1164.all;

entity half_adder_simple_tb is

end half_adder_simple_tb;

architecture tb of half_adder_simple_tb is

signal a, b : std_logic; -- inputs

signal sum, carry : std_logic; -- outputs

begin

-- connecting testbench signals with half_adder.vhd

UUT : entity work.half_adder port map (a => a, b => b, sum => sum, carry => carry);

-- half_adder and the TB must be in the same directory

STIM: process

constant period: time := 50 ns;

begin

a <= '0';

b <= '0';

wait for period;

assert ((sum = '0') and (carry = '0')) -- expected output

-- error will be reported if sum or carry is not 0

report "test failed for input combination 00" severity error;

a <= '0';

b <= '1';

wait for period;

assert ((sum = '1') and (carry = '0'))

report "test failed for input combination 01" severity error;

a <= '1';

b <= '0';

wait for period;

assert ((sum = '1') and (carry = '0'))

report "test failed for input combination 10" severity error;

a <= '1';

b <= '1';

wait for period;

assert ((sum = '0') and (carry = '1'))

report "test failed for input combination 11" severity error;

-- Fail test

a <= '0';

b <= '1';

wait for period;

assert ((sum = '0') and (carry = '1'))

report "test failed for input combination 01 (fail test)" severity error;

wait; -- indefinitely suspend process

end process;

end tb ;이 테스트벤치코드는 half_adder.vhd 파일에서 정의된 half_adder라는 이름의 엔티티를 테스트합니다.

이 테스트 벤치에서는 입력신호 a,b와 출력신호 sum,carry를 정의합니다.

UUT라는 이름으로 half_adder엔티티를 인스턴스화 하고, 이를 테스트벤치의 입력과 출력신호와 연결합니다.

이것을 통하여 입력신호를 half_adder로 전달하고, 출력 신호를 테스트벤치로 가져올 수 있습니다.

STIM프로세스는 테스트벤치의 핵심입니다. 이 프로세스는 입력신호 a,b에 값을 할당하고, 이를 half_adder에 전달하여 출력신호 sum,carry를 측정합니다. 이후 예상 출력값과 실제 출력값이 일치하는지 확인하기 위해 assert문을 사용합니다.

여기서는 입력신호 a,b가 00,01,10,11순서로 변화하며, 각각의 대해 예상 출력값을 assert문으로 검증합니다.

그리고 fail test를 실행하여 예상출력값과 다른 경우의 assert문도 확인합니다.

'Computer_logic' 카테고리의 다른 글

| Modulo M counter (0) | 2023.04.06 |

|---|---|

| Mealy & Moore VHDL code (0) | 2023.04.05 |

| Mealy FSM & Moore FSM (0) | 2023.04.05 |

| TCP Congestion control (0) | 2022.11.09 |

| FLOW control (0) | 2022.11.09 |