Finite State Machines(유한상태기계)는 주어진 입력에 따라 사전 정의된 동작을 수행하는 자동화된 기계입니다. FSM은 입력이 발생할 때 현재 상태에서 다음 상태로 전환하고, 출력을 생성합니다. FSM은 상태, 입력 및 출력에 대한 추상화된 모델을 사용하여 디지털 논리 회로 설계를 기술하는 데 자주 사용됩니다.

FSM은 두 가지 종류가 있습니다. Mealy 모델과 Moore 모델입니다. Mealy 모델에서는 상태 전이와 출력 값이 입력 및 현재 상태에 따라 결정됩니다. 반면에 Moore 모델에서는 상태 전이와 출력 값이 현재 상태에만 의존합니다. 각각의 모델은 특정 문제를 해결하기 위해 사용됩니다.

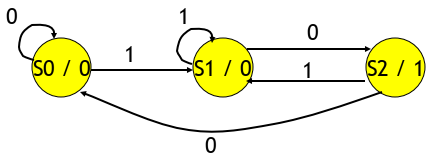

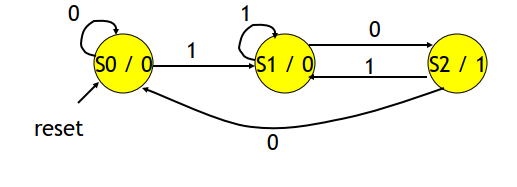

무어 모델은 상태 전이와 출력 값이 서로 독립적입니다. 즉, FSM의 현재 상태만으로 출력 값을 결정합니다. 따라서 무어 모델에서는 출력 값이 현재 상태에 대한 함수로 표현됩니다. 예를 들어, 현재 상태가 "정지"일 때 "정지" 라는 출력을 내보냅니다. 무어 모델은 출력 값이 안정적이며, 회로 구성이 단순하며 구현이 쉬워서 자주 사용됩니다.

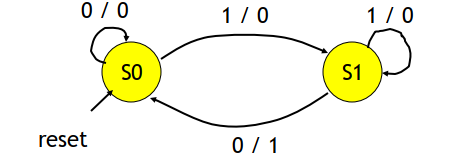

밀리 모델은 상태 전이와 출력 값이 입력 값에 따라 결정됩니다. 따라서 밀리 모델에서는 출력 값이 입력 값과 현재 상태에 대한 함수로 표현됩니다. 예를 들어, 입력 값이 "1"이면 현재 상태에 따라 "1" 또는 "0"을 출력합니다. 밀리 모델은 출력 값이 동적이며, 상태 전이에 대한 피드백을 받아 반응성을 높일 수 있습니다. 하지만 회로 구성이 복잡하며, 디자인이 어렵습니다.

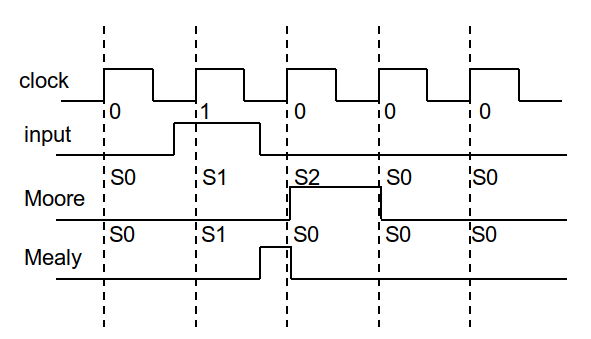

이 타이밍 다이어그램을 통하여 무어머신과 밀리머신의 state는 인풋에 따라서 즉각적으로 변하지만 출력값은 밀리머신은인풋값이 0으로 떨어짐과 동시에 바로 아웃풋으로 1이 출력되는것을 볼수있고 그에 반하여 무어머신은 클락에 동기화하여 스테이트가 변한 직후에 아웃풋이 변하는걸 관찰할 수 있습니다.

다음은 무어머신과 밀리머신의 쿼터스의 vhdl을 통한 코드작성입니다.

TYPE state IS (S0, S1, S2);

SIGNAL Moore_state: state;

U_Moore: PROCESS (clock, reset)

BEGIN

IF(reset = ‘1’) THEN

Moore_state <= S0;

ELSIF (clock = ‘1’ AND clock’event) THEN

CASE Moore_state IS

WHEN S0 =>

IF input = ‘1’ THEN

Moore_state <= S1;

ELSE

Moore_state <= S0;

END IF;

WHEN S1 =>

IF input = ‘0’ THEN

Moore_state <= S2;

ELSE

Moore_state <= S1;

END IF;

WHEN S2 =>

IF input = ‘0’ THEN

Moore_state <= S0;

ELSE

Moore_state <= S1;

END IF;

END CASE;

END IF;

END PROCESS;

Output <= ‘1’ WHEN Moore_state = S2 ELSE ‘0’;위 코드를 잘 보면 state의 상태들을 제시하고 clock과 reset을 동기화 해주었습니다.

만약 reset이 1이라면 초기 스테이트인 S0로 이동하도록 해주었으며, CLOCK이 1이면 무어머신의 현재 스테이트가 S0라면 인풋값으로 1이들어오면 스테이트는 S1로 설정이되게하고, 그게아니라면 S0으로 설정이되게 하였습니다.

만약 현재 스테이트가 S1이라면 인풋값으로 0이 들어온다면 스테이트를 S2로 설정을 해주고 그게 아니라면 S1으로 설정을 하게 하였습니다.

만약 현재 스테이트가 S2라면 인풋값으로 0이 들어오면 스테이트를 S0로 옮겨지게 설정을 해주고 그게 아니라면 S1으로 설정을 해주게 하였으며 맨 밑 코드에 나와있는것처럼 아웃풋 설정은 무어머신의 현재 스테이트가 S2라면 1을 출력하고 그게 아니라면 0을 출력하게 설정이 된걸 볼 수 있습니다.

TYPE state IS (S0, S1);

SIGNAL Mealy_state: state;

U_Mealy: PROCESS(clock, reset)

BEGIN

IF(reset = ‘1’) THEN

Mealy_state <= S0;

ELSIF (clock = ‘1’ AND clock’event) THEN

CASE Mealy_state IS

WHEN S0 =>

IF input = ‘1’ THEN

Mealy_state <= S1;

ELSE

Mealy_state <= S0;

END IF;

WHEN S1 =>

IF input = ‘0’ THEN

Mealy_state <= S0;

ELSE

Mealy_state <= S1;

END IF;

END CASE;

END IF;

END PROCESS;

Output <= ‘1’ WHEN (Mealy_state = S1 AND input = ‘0’) ELSE ‘0’;이 밀리머신을 구현한 VHDL코드를 보면 알겠듯이 아까 무어머신과는 동일하게 스테이트 설정을 해주고 스테이트 이동도 인풋에 따라서 비슷하게 구현이 되었습니다. 근데 여기에서 마지막에 아웃풋을 설정해주는 코드를 유심히보면 알겠지만

현재 스테이트의 값과 다음 인풋에 따라서 아웃풋이 결정된다는걸 알수있습니다.

만약 현재의 밀리머신의 스테이트값이 S1이고 인풋이 0이라면 바로 아웃풋은 1이고 그게 아니라면 0이라고 해석이됩니다.

다음은 좀 더 자세하게 무어머신과 밀리머신의 VHDL코드에 대하여 알아보도록 하겠습니다.

'Computer_logic' 카테고리의 다른 글

| Testbench (0) | 2023.04.06 |

|---|---|

| Mealy & Moore VHDL code (0) | 2023.04.05 |

| TCP Congestion control (0) | 2022.11.09 |

| FLOW control (0) | 2022.11.09 |

| TCP에러컨트롤 (0) | 2022.11.09 |